## TABLE OF CONTENTS

| Ι.   | Overview of the Connector                   | . 3 |

|------|---------------------------------------------|-----|

|      | Routing Strategies                          |     |

|      | Compliant Pin Via Construction              |     |

|      | Plating Validation                          | 6   |

|      | Transmission Line Configuration             | . 8 |

|      | Anti-pad Size                               | . 8 |

|      | Differential Trace to Signal Pad Attachment | . 9 |

|      | Routing Examples                            |     |

| III. | Crosstalk                                   | 11  |

| IV.  | Backdrilling                                | 12  |

| <u>REVISION:</u> | ECR/ECN INFORMATION:<br>EC No: UCP2014-4273<br>DATE: 2014/04/15 | TITLE:<br>IMPACT<br>CONNEC |                                   | <u>SHEET No.</u><br>2 of 12 |                   |  |

|------------------|-----------------------------------------------------------------|----------------------------|-----------------------------------|-----------------------------|-------------------|--|

| DOCUMEN          | T NUMBER:                                                       | CREATED / REVISED BY:      | TED / REVISED BY: CHECKED BY: APP |                             |                   |  |

| A                | S-76060-990                                                     | T. ELO                     | T. ELO                            | R. NEI                      | LSON              |  |

|                  |                                                                 |                            |                                   | FILENA                      | AME: PS74031C.DO0 |  |

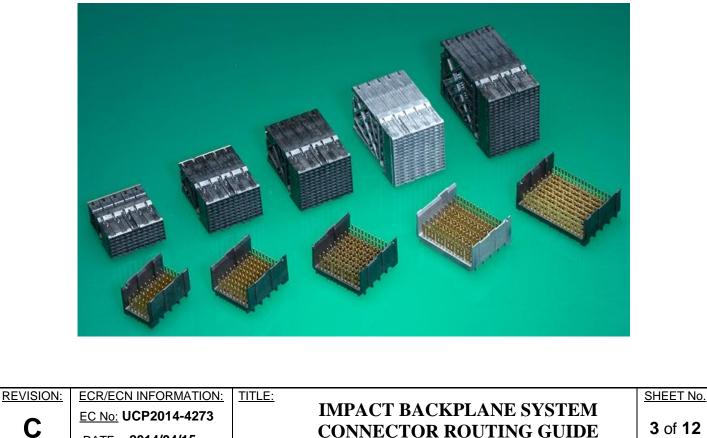

### **OVERVIEW OF THE CONNECTOR**

The Impact backplane connector system provides data rates up to 25 Gbps and superior signal density up to 80 differential pairs per inch. The Impact System's broad-edge-coupled technology enables low cross-talk and high signal bandwidth while minimizing channel performance variation across every differential pair within the system.

Molex's Impact System offers multiple compliant-pin design options on both the daughter card and backplane connectors, providing customers ultimate flexibility to optimize their designs for superior mechanical and electrical performance.

The Impact backplane connector system is designed for traditional backplane and/or midplane architectures to meet the growing demands of next-generation telecommunication and data networking equipment manufacturers. The Impact backplane connector system is offered in 2 pair, 3 pair, 4 pair, 5 pair, and 6 pair traditional BP header and DC connector versions, with a complete range of guidance, power, coplanar, mezzanine, and high performance cable solutions.

3 of 12

С

|              | C DATE: 2014/04/15 CONNECTOR ROUTING GUIDE |                       |             |               |         |  |  |  |  |  |

|--------------|--------------------------------------------|-----------------------|-------------|---------------|---------|--|--|--|--|--|

| DOCUMENT     | <u> NUMBER:</u>                            | CREATED / REVISED BY: | CHECKED BY: | <u>APPROV</u> | /ED BY: |  |  |  |  |  |

| AS-76060-990 |                                            | T. ELO                | T. ELO      | R. NEL        | SON     |  |  |  |  |  |

|              |                                            |                       |             |               |         |  |  |  |  |  |

FILENAME: PS74031C.DO

## **II. ROUTING STRATEGIES**

'nolèx®

## A) Compliant Pin Via Constructions

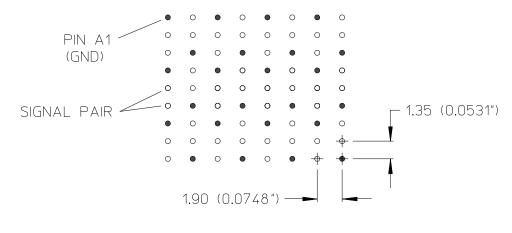

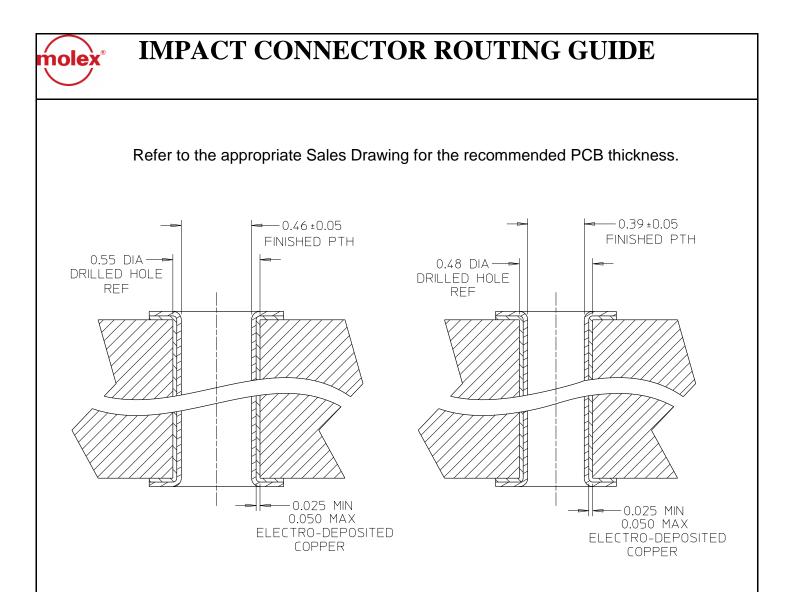

The Impact connector system is available in two distinct compliant pin sizes, designed for 0.39mm diameter and 0.46mm diameter plated-thru-holes. The pcb hole pattern is identical between the backplane and daughter card. A simple 1.90 by 1.35mm (.075 by .053") compliant pin grid, as shown in Figure 1, on both backplane and daughter card, reduces PCB routing complexity.

**Figure 1** Connector Hole Pattern (BP)

The recommended pad stack for the two hole sizes are contained in Table A. All non-functional pads are to be removed for high speed applications.

|           | FEATURE              | 0.39mm PTH<br>NOMINAL DIA                               | 0.46mm<br>NOMINAI                                  |          |                  |  |  |  |

|-----------|----------------------|---------------------------------------------------------|----------------------------------------------------|----------|------------------|--|--|--|

|           | Finished hole        | 0.39mm (15.3 mil                                        | ) 0.46mm (1                                        | 8 mil)   |                  |  |  |  |

|           | Drill                | 0.48mm (18.9 mil                                        | ) 0.55mm (2 <sup>-</sup>                           | 1.7 mil) |                  |  |  |  |

|           | Interior Pad         | 0.71mm (28 mil)                                         | 0.80mm (31                                         | 1.5 mil) |                  |  |  |  |

|           | Top Layer Pad        | 0.80mm (31.5 mil                                        | ) 0.80mm (3                                        | 1.5mil)  |                  |  |  |  |

|           | Bottom Layer Pad     | 0.71mm (28 mil)                                         | 0.80mm (31                                         | 1.5 mil) |                  |  |  |  |

|           | Anti-pad             | Anti-pad See Figure 2 (page 6) See Figure 2 (page 6)    |                                                    |          |                  |  |  |  |

|           |                      | <b>Table A</b><br>Pad Stack Dimer                       | nsions                                             |          |                  |  |  |  |

| REVISION: | ECR/ECN INFORMATION: | TITLE:                                                  |                                                    |          | SHEET No.        |  |  |  |

| <b>^</b>  | EC No: UCP2014-4273  |                                                         | IMPACT BACKPLANE SYSTEM<br>CONNECTOR ROUTING GUIDE |          |                  |  |  |  |

| С         | DATE: 2014/04/15     | CONNEC                                                  |                                                    |          |                  |  |  |  |

| DOCUMEN   | IT NUMBER:           | CREATED / REVISED BY: <u>CHECKED BY:</u> <u>APPROVE</u> |                                                    |          |                  |  |  |  |

| Α         | S-76060-990          | T. ELO                                                  | T. ELO                                             | R. NEL   | SON              |  |  |  |

|           |                      |                                                         |                                                    | FILENA   | ME: PS74031C.DOC |  |  |  |

#### Notes:

- 1. The finished PTH size is the critical feature for proper performance of the compliant pin terminal. It is important to maintain a reasonable Cpk to this feature.

- 2. The reference drill sizes listed are recommended based on Molex's qualification to achieve the finished PTH size. Depending upon the specific manufacturer's plating process, a different drill size can be used to achieve the required finished PTH size.

- 3. The typical drill hole tolerance is +/-0.013mm.

| REVISION:    | ECR/ECN INFORMATION:    | TITLE:                |                         |        | SHEET No.         |  |  |  |  |  |  |  |

|--------------|-------------------------|-----------------------|-------------------------|--------|-------------------|--|--|--|--|--|--|--|

|              | EC No: UCP2014-4273     |                       | IMPACT BACKPLANE SYSTEM |        |                   |  |  |  |  |  |  |  |

| C            | <u>DATE:</u> 2014/04/15 | CONNEC                | CONNECTOR ROUTING GUIDE |        |                   |  |  |  |  |  |  |  |

| DOCUMEN      | T NUMBER:               | CREATED / REVISED BY: | CHECKED BY:             | APPRO\ | /ED BY:           |  |  |  |  |  |  |  |

| AS-76060-990 |                         | T. ELO                | T. ELO T. ELO R. NELS   |        |                   |  |  |  |  |  |  |  |

|              |                         |                       |                         | FILENA | AME: PS74031C.DOC |  |  |  |  |  |  |  |

#### **PLATING VALIDATION**

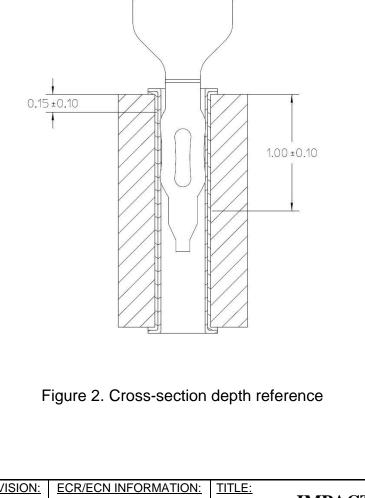

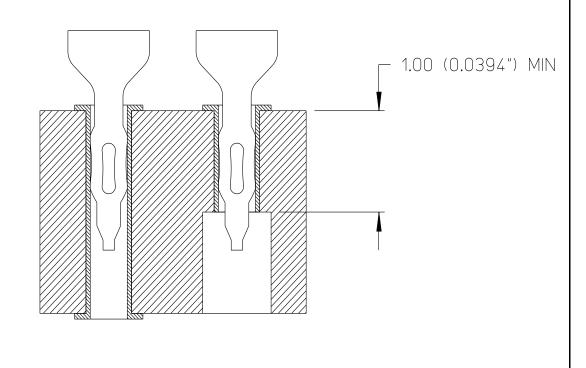

The requirements of finish hole size and copper barrel thickness <u>must</u> be maintained in the via from the board surface (applied connector side) through 1.00 mm depth to guarantee the mechanical performance of the compliant pin (see Figure 2).

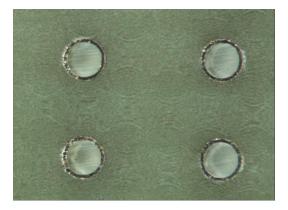

Validation of the plated through hole must be achieved through cross-sectioning. Sectioning radially (Figure 4) provides information regarding the drill size, copper barrel thickness, and finish plating barrel thickness. Molex recommends cross-sectioning radially to the depths of 0.15 mm and 1.00 mm to ensure a uniform plated hole meets the requirements provided in this document.

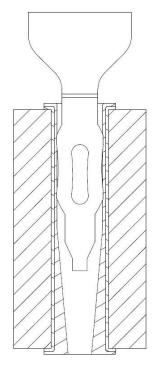

Longitudinal sectioning (Figure 5) will confirm plating uniformity, which must be held to the depths given for proper compliant pin performance. Non-uniformity beyond the 1.00 mm depth requirement will not affect the compliant pin mechanical performance (see Figure 3). Please see the next page for cross section examples.

Figure 3. Non-Uniform Plating

| REVISION:<br>C                   | ECR/ECN INFORMATION:<br>EC No: UCP2014-4273<br>DATE: 2014/04/15 | TITLE:IMPACT BACKPLANE SYSTEM<br>CONNECTOR ROUTING GUIDESHEET No6 of 12 |                                     |                  |  |  |  |  |  |  |

|----------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------|------------------|--|--|--|--|--|--|

| DOCUMENT NUMBER:<br>AS-76060-990 |                                                                 | CREATED / REVISED BY:<br>T. ELO                                         | <u>CHECKED BY:</u><br><b>T. ELO</b> | APPRO\<br>R. NEI |  |  |  |  |  |  |

| FIL ENAME: PS74031C DOC          |                                                                 |                                                                         |                                     |                  |  |  |  |  |  |  |

#### **CROSS-SECTION EXAMPLES**

Figure 4. Radial Cross-section of PC Board to validate dimensions.

Figure 5. Longitudinal Section verifying plating uniformity of hole.

It is Molex's recommendation that the PCB supplier provide board cross-sections confirming dimensional conformity to the requirements established in this document. A dimensional report and associated IPC compliance requirements should be provided with every lot of board material provided to the customer. The board supplier should target an average finish plated hole size (of 0.39 mm or 0.46 mm) to optimize the performance of the connector at board installation.

| REVISION:    | ECR/ECN INFORMATION: | TITLE:                |                                                           |        | SHEET No.         |  |  |  |  |  |  |  |

|--------------|----------------------|-----------------------|-----------------------------------------------------------|--------|-------------------|--|--|--|--|--|--|--|

|              |                      |                       | IMPACT BACKPLANE SYSTEM<br>CONNECTOR ROUTING GUIDE7 of 12 |        |                   |  |  |  |  |  |  |  |

|              | DATE: 2014/04/15     | CONNEC                | CONNECTOR ROUTING GUIDE 7 01 12                           |        |                   |  |  |  |  |  |  |  |

| DOCUMEN      | T NUMBER:            | CREATED / REVISED BY: | /ED BY:                                                   |        |                   |  |  |  |  |  |  |  |

| AS-76060-990 |                      | T. ELO                | T. ELO T. ELO R. NELSON                                   |        |                   |  |  |  |  |  |  |  |

|              |                      |                       |                                                           | FILENA | AME: PS74031C.DOC |  |  |  |  |  |  |  |

### B) Transmission Line Configuration

Coupled differential strip lines are the recommended transmission lines for high speed applications. For a specific system differential impedance (i.e., 100 or 85 ohms), different trace width and spacing can be accommodated for any preferred pcb stack up configuration. Designers often consider particular common mode impedance based on factors such as skew, fabrication consistency, and density. Any particular choice of trace width and spacing ultimately affects the routing configuration within the routing channel. In high speed applications, the routing channel is a defined channel between the connector column pins.

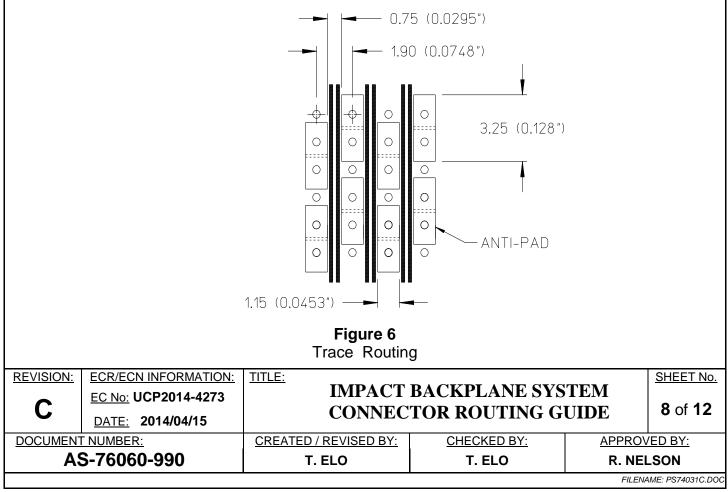

## C) Anti-pad Size

For most high-speed applications, one needs to maximize the anti-pad width (between columns) and length (between rows). The width of the anti-pad is affected by the following:

- 1) Trace width and spacing

- 2) Pair to pair spacing

- 3) Top and bottom ground strips to trace edge spacing

The length of the anti-pad is limited by the distance and the construction of ground pin vias. The anti-pads shown in Figure 6 are based on a 7 mil trace width and spacing and a 4 mil registration buffer (top and bottom ground strips edge to trace outer edge).

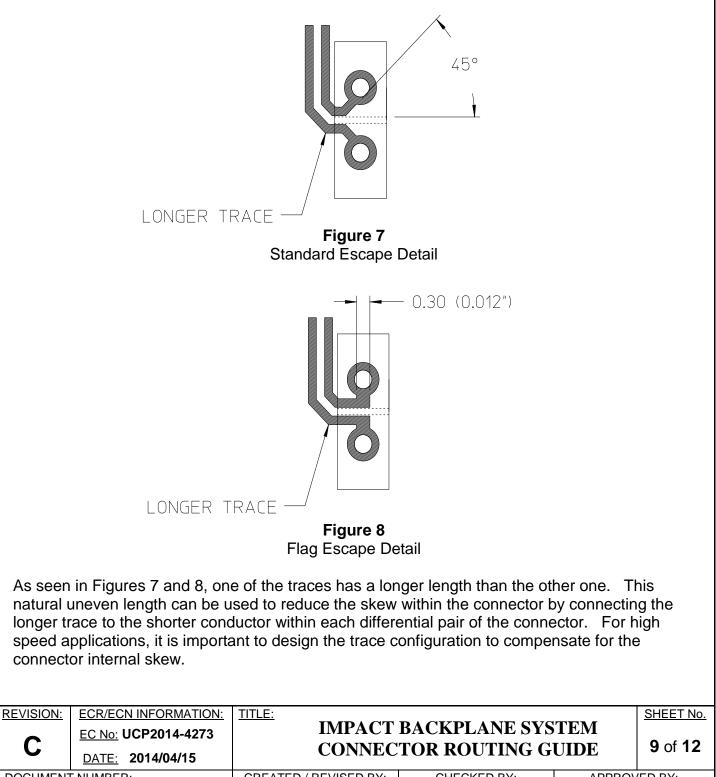

#### D) Differential Trace to Signal Pad Attachment

There are several ways to connect the differential traces to their corresponding signal pads. Two possible methods are illustrated in Figures 7 and 8.

| DOCUMENT NUMBER: | CREATED / REVISED BY: | CHECKED BY: | APPROVED BY:          |

|------------------|-----------------------|-------------|-----------------------|

| AS-76060-990     | T. ELO                | T. ELO      | R. NELSON             |

|                  |                       |             | EILENAME: PS74031C DO |

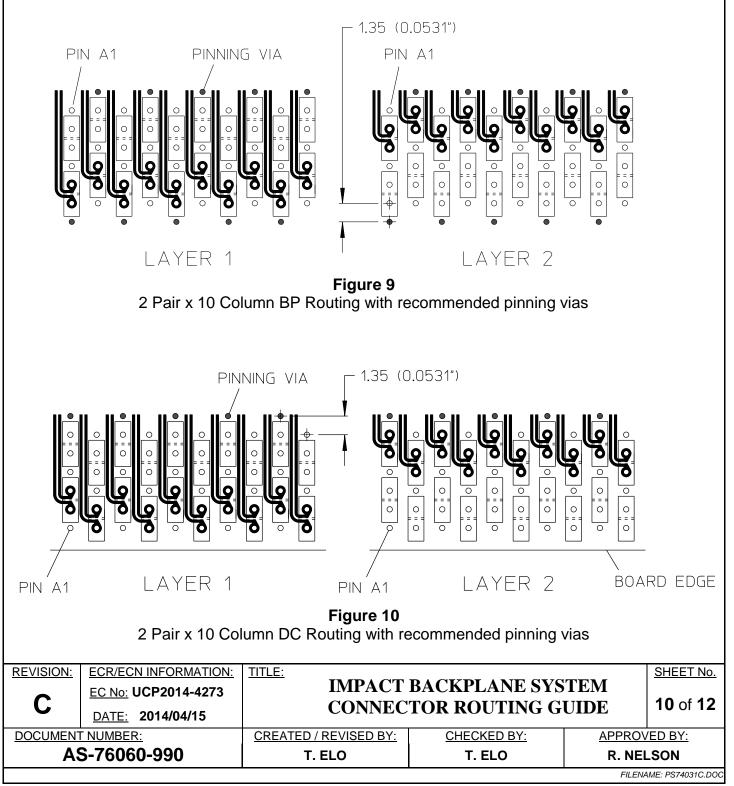

### E) Routing Examples

It is recommended to use ground pinning vias to improve the crosstalk performance of the board.

Figure 9 shows the recommended pinning vias and routing example for the Impact 2 Pair backplane connector. Typically, the size of the pinning vias is the same size as the connector vias. Figure 10 shows the recommended pinning vias for the Impact 2 Pair daughtercard.

## III. CROSSTALK

Crosstalk mitigation is a critical element of high speed system design. There are some simple considerations to reduce crosstalk in many systems. These include the following:

- 1. Separate transmit and receive transmission lines. If transmit and receive transmission lines need to be placed on the same layer, separate them with extra space. It is recommended to place them on separate routing layers.

- 2. Separate transmit and receive vias. Group the TX and RX differential vias in blocks in rows or columns and, if possible, separate them with slow or DC signal lines.

Tables C and D show two examples of TX and RX grouping.

|   | 1  | 2  | 3  | 4  | 5    | 6  | 7  | 8  | 9  | 10 |

|---|----|----|----|----|------|----|----|----|----|----|

| Α | G  | ΤX | G  | ΤX | G    | LS | G  | RX | G  | RX |

| В | ΤX | ΤX | ΤX | ΤX | LS   | LS | RX | RX | RX | RX |

| С | ΤX | G  | ΤX | G  | LS   | G  | RX | G  | RX | G  |

| D | G  | ΤX | G  | ΤX | G    | LS | G  | RX | G  | RX |

| Ε | ΤX | ΤX | ΤX | ΤX | LS   | LS | RX | RX | RX | RX |

| F | ΤX | G  | ΤX | G  | LS   | G  | RX | G  | RX | G  |

| G | G  | ΤX | G  | ΤX | G    | LS | G  | RX | G  | RX |

| Н | ΤX | ΤX | ΤX | ΤX | LS   | LS | RX | RX | RX | RX |

| J | ΤX | G  | ΤX | G  | LS   | G  | RX | G  | RX | G  |

| Κ | G  | ΤX | G  | ΤX | G    | LS | G  | RX | G  | RX |

| L | ΤX | ΤX | ΤX | ΤX | LS   | LS | RX | RX | RX | RX |

| Μ | ΤX | G  | ΤX | G  | LS   | G  | RX | G  | RX | G  |

|   |    |    |    | Та | able | С  |    |    |    |    |

TX RX grouping separated by low speed (LS) signal columns

|                        | -                  |                         |       |       |      | -           |       |       | . ,  | -                  |       |         |  |  |           |

|------------------------|--------------------|-------------------------|-------|-------|------|-------------|-------|-------|------|--------------------|-------|---------|--|--|-----------|

|                        |                    | 1                       | 2     | 3     | 4    | 5           | 6     | 7     | 8    | 9                  | 10    |         |  |  |           |

|                        | Α                  | G                       | ΤX    | G     | ΤX   | G           | ΤX    | G     | ΤX   | G                  | ΤX    |         |  |  |           |

|                        | В                  | ΤX                      | ΤX    | ΤX    | ΤX   | ΤX          | ΤX    | ΤX    | ΤX   | ΤX                 | ΤX    |         |  |  |           |

|                        | С                  | ΤX                      | G     | ΤX    | G    | ΤX          | G     | ΤХ    | G    | ΤХ                 | G     |         |  |  |           |

|                        | D                  | G                       | ΤX    | G     | ΤX   | G           | ΤX    | G     | ΤX   | G                  | ΤX    |         |  |  |           |

|                        | Ε                  | ΤX                      | ΤX    | ΤX    | ΤX   | ΤX          | ΤX    | ΤX    | ΤX   | ΤX                 | ΤX    |         |  |  |           |

|                        | F                  | ΤX                      | G     | ΤX    | G    | ΤX          | G     | ΤX    | G    | ΤX                 | G     |         |  |  |           |

|                        | G                  | G                       | RX    | G     | RX   | G           | RX    | G     | RX   | G                  | RX    |         |  |  |           |

|                        | Н                  | RX                      | RX    | RX    | RX   | RX          | RX    | RX    | RX   | RX                 | RX    |         |  |  |           |

|                        | J                  | RX                      | G     | RX    | G    | RX          | G     | RX    | G    | RX                 | G     |         |  |  |           |

|                        | K                  | G                       | RX    | G     | RX   | G           | RX    | G     | RX   | G                  | RX    |         |  |  |           |

|                        | L                  | RX                      | RX    | RX    | RX   | RX          | RX    | RX    | RX   | RX                 | RX    |         |  |  |           |

|                        | Μ                  | RX                      | G     | RX    | G    | RX          | G     | RX    | G    | RX                 | G     |         |  |  |           |

|                        |                    |                         |       |       |      | able        |       |       |      |                    |       |         |  |  |           |

|                        | TX RX g            | roup                    | ing t | by ro | ws ( | sepa        | arate | ed by | def  | ined               | grour | nds)    |  |  |           |

| REVISION: ECR/ECN INFO | ORMATION           | <u>1:</u>   <u>T</u>    | ITLE: |       |      |             |       |       |      |                    |       |         |  |  | SHEET No. |

| EC No: UCP2            |                    |                         |       |       |      | -           |       | -     |      | NE S               |       |         |  |  |           |

| <u>DATE:</u> 2014      |                    | CONNECTOR ROUTING GUIDE |       |       |      |             |       |       | £    | 11 of 12           |       |         |  |  |           |

| DOCUMENT NUMBER:       |                    | CREATED / REVISED BY:   |       |       |      | CHECKED BY: |       |       |      | APPROVED BY:       |       | VED BY: |  |  |           |

| AS-76060-99            |                    | T. ELO T. ELO R. NELSON |       |       |      |             |       |       | LSON |                    |       |         |  |  |           |

|                        | FILENAME: PS74031C |                         |       |       |      |             |       |       |      | IAME: PS74031C.DOC |       |         |  |  |           |

#### IV. BACKDRILLING

For high speed signals, it may be necessary to remove excess via stub below the pcb signal layer. This is accomplished by backdrilling the plated via with a larger diameter drill to remove the undesirable excess via. The Impact compliant pin design allows for backdrilling to within 1mm of the top surface of the PCB.

Figure 11 Backdrill Specification